A logic low input causes the t flip flop to maintain its current output state.

T flip flop counter truth table.

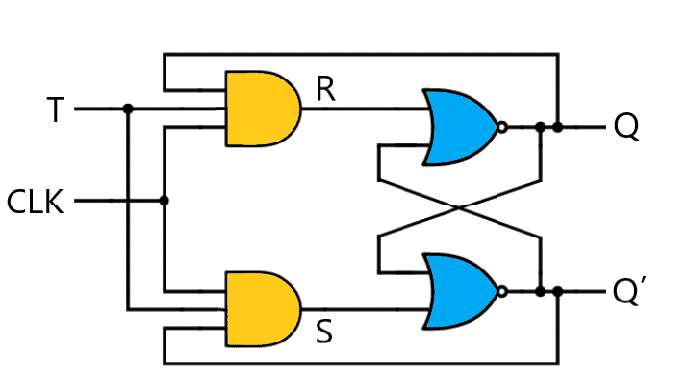

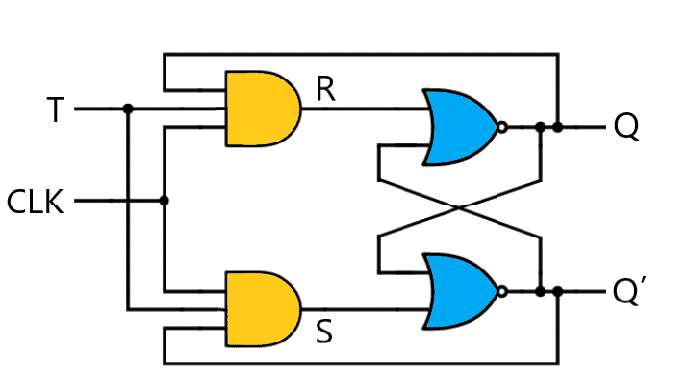

If the output q 0 then the upper nand is in enable state and lower nand gate is in disable condition.

The q and q represents the output states of the flip flop.

From sr or jk to t.

This modified form of jk flip flop is obtained by connecting both inputs j and k together.

With such configuration the upper circuit shown in the image became modulo 10 or a decade counter.

To design the combinational circuit of valid states following truth table and k map is drawn.

To design a synchronous up counter first we need to know what number of flip flops are required.

Rest of the states are invalid.

From the above truth table we draw the k maps and get the expression for the mod 6 asynchronous counter.

The clock signal is directly applied to the first t flip flop.

This flip flop has only one input along with the clock input.

According to the table based on the input the output changes its state.

A t flip flop is like jk flip flop.

These are basically a single input version of jk flip flop.

Truth table of t flip flop.

As mentioned earlier t flip flop is an edge triggered device.

You can modify the input to output relationship of an existing flip flop by adding logic gates and appropriate interconnections.

The t flip flop is the modified form of jk flip flop.

All these flip flops are negative edge triggered but the outputs change asynchronously.

Introduction to t flip flop contribute.

Here is the same information in truth table form.

The truth table of a t flip flop is shown below.

Mod 6 asynchronous counter will require 3 flip flops and will count from 000 to 101.

Thus n 3.

The 3 bit asynchronous binary up counter contains three t flip flops and the t input of all the flip flops are connected to 1.

When the flip flops reset the output from d to a all became 0000 and the output of nand gate reset back to logic 1.

Which means that this is a counter with three flip flops which means three bits having eight stable states 000 to 111 and capable of counting eight events or up to the decimal number 1 7.

The truth table of decade counter is shown in the next table.

From the equation above.

For example consider a t flip flop made of nand sr latch as shown below.